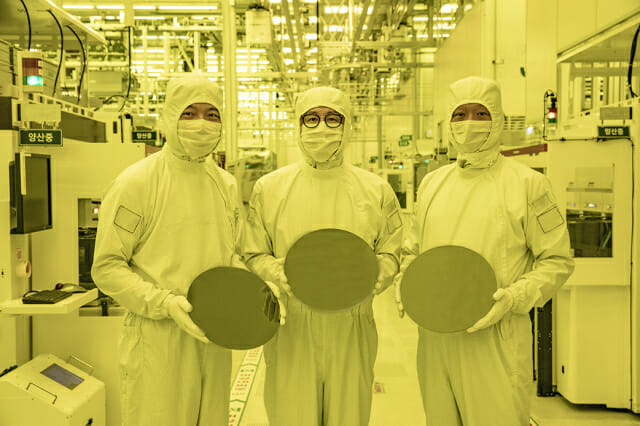

AI HPC 시장 수요증가로 첨단 공정 개발 가속화

반도체 파운드리업체들이 1나노미터 첨단 공정 기술 경쟁에 돌입했다.

지난해 삼성전자와 대만 TSMC가 선도적으로 3나노 공정 양산을 시작한데 이어, 후발주자인 미국 인텔과 일본 라피더스까지 가세하면서 파운드리 업계는 2025년 양산을 목표로 2나노 공정 기술을 준비 중이다.

이런 상황에서 인공지능(AI) 반도체 수요가 급증하자 파운드리 업계는 2027년 1나노 공정 양산을 시작한다는 계획을 잇달아 발표했다.

시장조사업체 트렌드포스는 "아직 2나노 공정으로 양산이 시작되지 않은 시점에 반도체 업계의 관심이 1나노급 칩으로 쏠리고 있다"라며 "AI와 고성능 컴퓨팅 같은 혁신에 힘입어 파운드리 시장에서 첨단 공정의 중요성이 더욱 커지고 있다"고 분석했다.

또 "2030년대 주류화될 것으로 예상되는 1나노 칩의 컴퓨팅 성능은 2나노보다 10~20% 앞설 것으로 예상된다"고 덧붙였다.

삼성전자는 지난해 6월 세계 최초로 3나노 공정 양산을 시작한 데 이어 2025년에는 2나노, 2027년에는 1.4나노 공정을 도입할 계획이다. 삼성전자는 지난 6월 미국 실리콘밸리에서 개최한 '삼성 파운드리 포럼'에서 "1.4나노 공정은 계획대로 2027년 양산한다"고 밝히며 1년 전 발표한 로드맵에 차질이 없다는 점을 강조했다.

삼성전자 1.4나노 칩 생산거점은 현재 선단 공정을 양산하는 평택 팹과 내년 가동을 목표로 건설 중인 테일러 팹이 유력하다. 다만, TSMC, 인텔 등 반도체 업계에서 첨단 공정 생산거점과 연구개발(R&D) 등은 자국에 유지하는 추세에 따라 삼성전자 또한 국내에서 1.4나노 공정 칩을 생산할 가능성이 높아 보인다.

TSMC는 지난달 말 대만 타이중에 위치한 중부과학단지에 1.4나노 팹(공장)을 건설하는 것을 확정했다. 대만 국가과학기술위원회(NSTC)는 내년 6월 해당 용지를 TSMC에 인도할 예정이다.

그동안 TSMC는 신규 첨단 공정 팹 건설을 위한 부지 선정에 난항을 겪어왔다. TSMC는 북부 룽탄 과학단지에 1.4나노 공정 팹을 2026년까지 건설해 2027년부터 양산에 들어갈 계획이었으나, 주민들의 반발로 결국 지난달 18일 포기를 결정했다. 차선책으로 TSMC는 타이중 과학단지에 팹 건설을 지난달 말 확정하면서 앞으로 1나노급 공정 기술 개발에 속도가 붙을 전망이다.

최근 일본 반도체 연합 라피더스도 1나노 공정 개발을 추진한다. 라피더스는 지난주 도쿄대학과 프랑스 전자정보기술연구소 레티(CEA-Leti)와 협력해 1나노 IC 설계 기초 기술을 공동 개발한다고 밝혔다. 도쿄대, 일본 국립대, 이화학연구소가 참여한 ‘최첨단 반도체 기술 센터(LSTC)’는 레티와 해당 내용을 담은 양해각서를 체결했고, 내년부터 인재 교류와 기술 공유를 시작할 예정이다.

또 라피더스는 미국 IBM과 협력해 2나노 공정 반도체 기술을 공동 개발에 이어 1나노 칩에 대한 기술 개발 협의도 고려중인 것으로 알려졌다. 라피더스는 2025년 2나노 공정으로 시험 생산을 목표로 하며, 2027년까지 대량 양산을 목표로 하고 있다. 1나노 칩은 2029~2030년에 양산할 것으로 전망된다.

라피더스는 정부 지원을 받고 토요타, 소니, 키옥시아, NTT, 소프트뱅크, NEC, 덴소, 미쓰비시UFJ은행 등 8개사가 2022년 11월에 설립한 반도체 회사다. 라피더스는 일본 북부 주요 섬인 홋카이도에 최첨단 반도체 공장을 건설 중이다. 네덜란드 극자외선(EUV) 반도체 장비 업체인 ASML은 내년 일본 훗카이도에 기술 지원 허브를 구축해 장비 지원, 유지 보수 및 검사 지원을 약속했다.

파운드리 시장 재진출을 선언한 인텔은 공격적인 투자로 2025년 가장 먼저 인텔 18A(1.8나노급) 공정으로 칩 양산을 시작한다는 목표를 세웠다. 인텔은 삼성전자와 TSMC가 2025년 2나노 양산, 2027년 1.4나노 양산한다는 계획 보다 앞서겠다는 포부다.

일각에서는 인텔이 아직 3나노도 생산하지 않는 단계에서 단숨에 TSMC와 삼성전자의 역전을 노리기는 현실적으로 어렵다는 의견이 나온다. TSMC와 삼성전자는 일찌감치 각각 2018년, 2019년에 7나노 공정 칩 양산을 시작했고, 지난해 3나노 공정 칩 양산을 시작했다. 반면 인텔은 올해 인텔4(7나노급)과 인텔 3(4나노급) 공정으로 칩 양산에 들어서면서 약 3~4년 뒤처졌기 때문이다.

이에 대한 반격으로 인텔은 지난 9월 미국 새너제이에서 개최한 '인텔 이노베이션 2023' 행사에서 1.8나노급인 18A 공정 반도체 웨이퍼 시제품을 깜짝 공개하기도 했다. 앞서 4월에는 영국 반도체 설계자산(IP) 업체와 18A 공정에서 설계 협력을 발표하기도 했다.